📚 기본 개념

- 아날로그 양은 연속적인 값을 가진다.

- 디지털 양에이산 값은 없다.

- 2진 체계에 2개의 숫자가 있다.

- 비트라는 용어는 binary digit의 약자이다.

- 양의 논리에서 LOW 레벨은 이진수 1을 표시한다.

- 주기 파영은 고정된 시간 간격으로 파형을 반복한다.

- 타이밍도는 2개 이상의 디지털 파형의 시간 관계를 나타낸다.

- AND 함수는 인버터라고 알려진 논리회로에 의해 구현된다.

- 플립플롭은 한 번에 2비트만 저장할 수 있는 쌍안정 논리회로이다.

- 두 가지 넓은 유형의 디지털 집적회로는 고정 기능 집적회로와 프로그램 가능한 집적회로이다.

⚙디지털 시스템의 장점

- 내외부 잡음에 강함

- 설계용이

- 프로그래밍으로 전체시스템 제어 가능, 규격 사양 변경에 쉽게 대응

- 정보저장 가공 용이

- 정보처리의 정확성과 정밀도 올림

- 비선형 처리, 병렬처리 가능

- 소형화, 저가격화

⚙디지털 정보 표현 단위

1nibble = 4bit

1 byte = 8bit

1 byte = 1charater

1byte로 영어 알파벳 하나 표현 가능, 한글은 2 byte 필요.

📚 용어 해설

- 게이트(gate) : AND 또는 OR 와 같은 기본 논리 연산을 수행하는 논리회로

- 논리(logic) : 디지털 전자공학에서, HIGH가 참을 나타내고 LOW가 거짓을 나타내는 게이트 회로에서 의사를 결정하는 능력

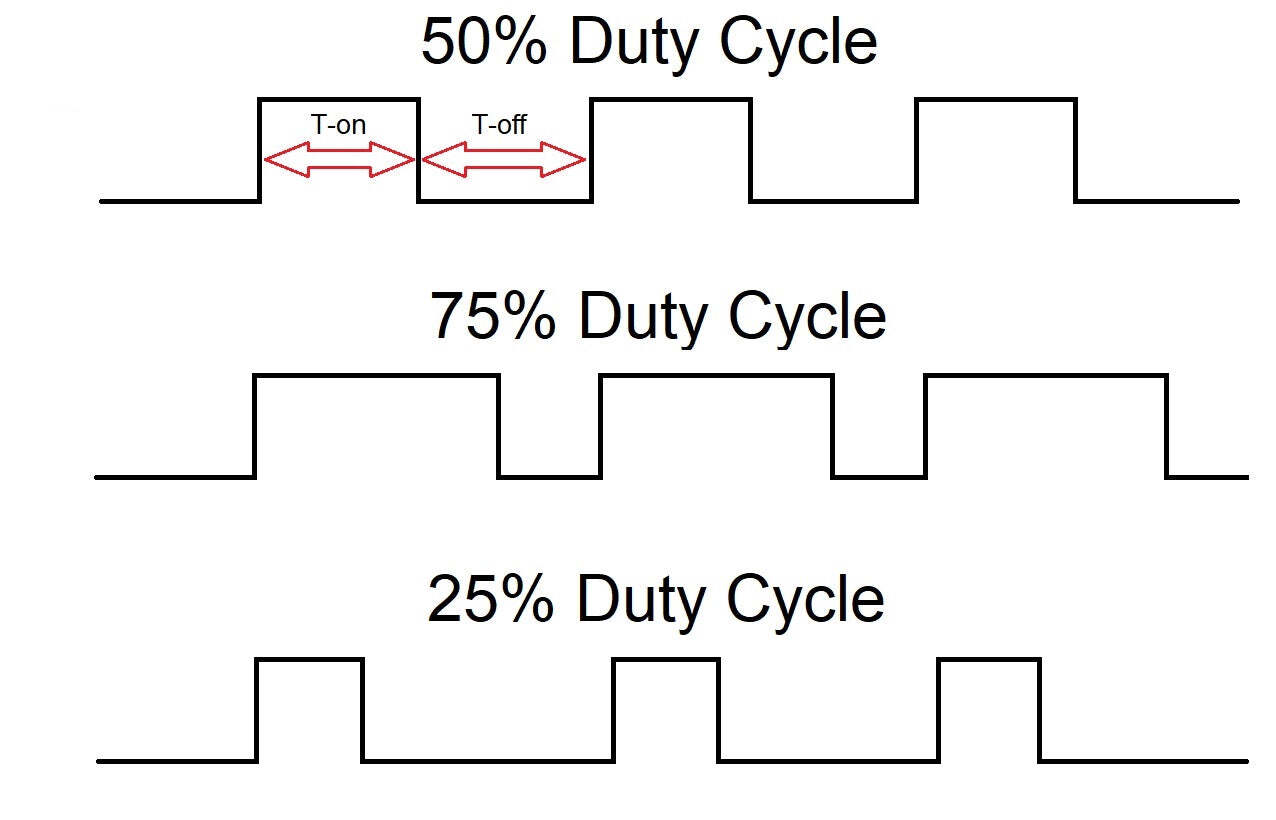

- 듀티 사이클(duty cycle) : 디지털 파형의 펄스 폭 대 주기의 비를 백분율로 표시한 것

- 비트(bit) : 1 또는 0일 수 있는 2진에서 한 숫자

- 인버터(inverter) : NOT 회로, HIGH를 LOW로 또는 그 반대로 변경하는 회로

- 임베디드 시스템(embedded system) : 일반적으로, 시스템 제어 목적으로 더 큰 시스템에 내장되는 프로세서와 같은 단일 목적의 시스템

- 집적회로(intergrated circuit, IC) : 모든 소자들이 매우 작은 크기의 반도체 재료로 된 단일 칩에 집약된 형태의 회로

- 컴파일러(compiler) : 설계 흐름 과정을 제어하고 논리적으로 테스트하거나 타깃 소자로 다운로드할 수 있는 형식으로 소스 코드를 오브젝트 코드로 변환하는 프로그램

- 클록(clock) : 디지털 시스템의 기본 타이밍 신호, 동작을 동기화하는 데 사용되는 주기 파형

- FPGA : filed-programmable gate array의 약자

- SPLD : simple programmable logic device의 약자

'Computer Science > 운영체제' 카테고리의 다른 글

| [OS] Introduction to Oprerating Systems (0) | 2023.06.22 |

|---|---|

| [디지털 공학] 조합 논리회로, 감가산기 (0) | 2022.04.22 |

| [디지털 공학] 불 대수와 논리 간략화 및 용어해설 (0) | 2022.04.21 |

| [디지털 공학] 논리 게이트 및 핵심 용어 (0) | 2022.04.21 |

| [디지털 공학] 수 체계, 연산, 코드 및 핵심 용어 (0) | 2022.04.21 |